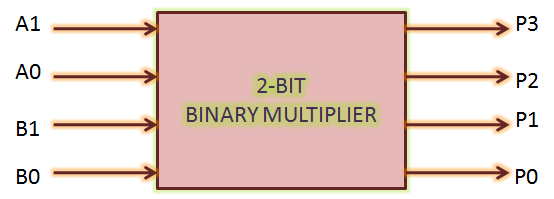

Binary Multiplier Block Diagram

Multiplier bit binary diagram block logic using gates two numbers vlsi figure multiplying 4 bit multiplier circuit diagram 4-bit multiplier design2

Block diagram of the multiplier: Two 8-bit operands a and b are

Binary multiplication partial sums during find multiplier bit Multiplier design2 Multiplier parallel proposed error composed

Multiplier bit binary using multiplication adders schematic calculator divider digital 4x4 adder logic gates electronics electricaltechnology possible multipliers types build

The block diagram for the 2-bit multiplierCourses:system_design:synthesis:combinational_logic:example_of_a Binary multiplierMultiplier array.

Multiplier vhdl bit logic diagram block example combinational synthesis courses system onlineA 4×4 bit array multiplier [12], [16]. Binary multipliersMultiplier asm chart.

![A 4×4 bit array multiplier [12], [16]. | Download Scientific Diagram](https://i2.wp.com/www.researchgate.net/profile/Maaruf_Ali/publication/333968081/figure/download/fig2/AS:772998130855936@1561308524096/A-44-bit-array-multiplier-12-16.png)

Block diagram of the proposed multiplier with one parallel

[binary] how to find partial sums during multiplication? : r/mathhelpBlock diagram of the multiplier: two 8-bit operands a and b are Design example binary multiplier. block diagram asm chartMultiplier operands two multiplied shifting.

Solved: chapter 18 problem 17p solutionBit multiplier binary circuit multiplication adder four three multiplicand bits solved gates addend Multiplier array unsigned2-bit binary multiplier : vlsi n eda.

Block diagram of binary multiplier

Block diagram of an unsigned 8-bit array multiplier.Solved the following circuit is a four-bit (multiplier) by Multiplier bit binary two circuit diagram block vlsiBinary multipliers.

2-bit binary multiplier : vlsi n eda .

Solved The following circuit is a four-bit (multiplier) by | Chegg.com

4 Bit Multiplier Circuit Diagram - Wiring Diagram and Schematics

Block Diagram of Binary Multiplier

The Block diagram for the 2-bit multiplier | Download Scientific Diagram

2-bit binary multiplier : VLSI n EDA

courses:system_design:synthesis:combinational_logic:example_of_a

Binary multipliers

Solved: Chapter 18 Problem 17P Solution | Fundamentals Of Logic Design

Block diagram of the multiplier: Two 8-bit operands a and b are